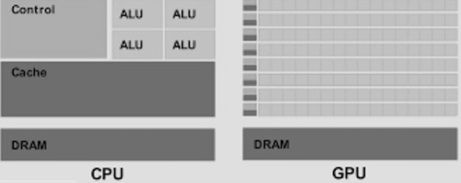

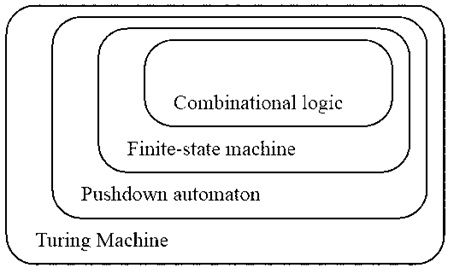

Järjestikune vooluring on loogiline vooluring, kus väljund sõltub nii sisendsignaali praegusest väärtusest kui ka varasemate sisendite järjestusest. Kuigi a kombineeritud vooluring on ainult praeguse sisendi funktsioon. Järjestikune vooluring on kombinatsioonahelast ja salvestuselemendist. järjestikused ahelad kasutavad praeguseid sisemuutujaid ja varasemaid sisendmuutujaid, mis on salvestatud ja edastavad andmed vooluringile järgmisel taktsükkel.

Järjestikuste vooluringide plokkskeem

Järjestikuste vooluahelate tüübid

The järjestikused ahelad liigitatakse kahte tüüpi

- Sünkroonne vooluring

- Asünkroonne ahel

Sünkroonsete järjestikuste vooluringide korral muutub seadme olek diskreetsetel aegadel vastuseks kellasignaalile. Asünkroonsetes ahelates muutub seadme olek vastuseks sisendite muutumisele.

Sünkroonsed ahelad

Sünkroonahelates on sisenditeks impulsid, millel on teatud piirangud impulsi laiusele ja leviku viivitusele. Seega saab sünkroonahelad jagada kellaga ja kellata või impulssjärgseteks ahelateks.

Sünkroonne vooluring

Kellaga järjestikune vooluring

Kellaga järjestikustel vooluahelatel on mäluelementide jaoks klapid või riivitud riivid. Kõigi sisemiste olekumuutuste sünkroniseerimiseks on ühendatud perioodiline kell, mis on ühendatud vooluahela kõigi mäluelementide kella sisenditega. Seega kontrollib ja sünkroniseerib vooluahela tööd kella perioodiline impulss.

Cocked järjest

Kellaajata järjestikune vooluring

Ajamita järjestikune vooluahel vajab ahela oleku vaheldumiseks kahte järjestikust üleminekut vahemikus 0 kuni 1. Kellata režiimiga vooluring on mõeldud reageerima teatud kestusega impulssidele, mis ei mõjuta vooluahela käitumist.

Lukustamata järjestus

Sünkroonse loogika vooluring on väga lihtne. Loogika väravad mis teostavad andmetega toiminguid, vajavad sisendimuutustele reageerimiseks piiratud aja.

Asünkroonsed ahelad

Asünkroonsel vooluringil ei ole oleku sisemiste muutuste sünkroonimiseks kella signaali. Seega toimub olekumuutus otseses vastuses muutustele, mis esinevad primaarsetes sisendjoontes. Asünkroonne vooluahel ei vaja täpset ajastuse juhtimist plätud .

Asünkroonne ahel

Asünkroonse loogika kujundamine on keerulisem ja sellega on sünkroonse loogikaga võrreldes probleeme. Peamine probleem on see, et digitaalne mälu on tundlik nende sisendsignaalide jõudmise järjekorra suhtes, näiteks kui kaks signaali jõuavad üheaegselt klapini, siis milline olek vooluringi saab sõltuda sellest, milline signaal jõuab kõigepealt loogikavärav.

Asünkroonseid vooluahelaid kasutatakse sünkroonsüsteemide kriitilistes osades, kus süsteemi kiirus on esmatähtis, nagu näiteks mikroprotsessorid ja digitaalsed signaalitöötlusahelad .

Flip Flopi ahel

Flip-flop on järjestikune vooluring, mis valib sisendi ja muudab väljundit teatud ajahetkel. Sellel on kaks stabiilset olekut ja seda saab kasutada olekuteabe salvestamiseks. Ahela oleku muutmiseks rakendatakse signaale ühele või mitmele juhtimissisendile ja sellel on üks või kaks väljundit.

See on digitaalse elektroonilise süsteemi järjestikuse loogika põhiline salvestuselement ja põhilised ehituselemendid. Neid saab kasutada muutuja väärtuse arvestuse pidamiseks. Flip-flopi kasutatakse ka vooluahela funktsionaalsuse juhtimiseks.

RS flip

R-S flip-flop on kõige lihtsam flip-flop. Sellel on kaks väljundit, üks väljund on teise tagurpidi ja kaks sisendit. Kaks sisendit on Set ja Reset. Flip-flop kasutab põhimõtteliselt NAND-väravaid koos täiendava lubamisnõelaga. Vooluring annab väljundi ainult siis, kui lubamisnõel on kõrge.

Blokeeri skeem

SR Flip Flopi plokkskeem

Vooluringi skeem

SR klapp-skeemi skeem

SR Flip Flopi tõetabel

SR Flip Flopi tõetabel

JK Flip Flop

JK flip-flop on üks olulisi plätusid. Kui J ja K sisendid on üks ja kella rakendamisel muutub väljund olenemata varasemast olekust. Kui J ja K sisendid on 0 ja kella rakendamisel ei muutu väljund. JK flip-flopis pole määramatut seisundit.

Vooluringi skeem

JK Flip Flop Circuit

JK Flip Flopi tõetabel

JK Flip Flopi tõetabel

D Flip Flop

D flip-flopil on üks andmerida ja kella sisend D flip-flop on SR flip-flopi lihtsustamine . D flip-flopi sisend läheb otse sisendisse S ja kompliment läheb sisendisse R. D sisend valitakse kogu kella impulsi vältel.

Vooluringi skeem

D flip flopi ahel

D flip flopi tõetabel

D flip flopi tõetabel

T Flip Flop

See on meetod RS-flip-flopi käigus leitud määramatu oleku vältimiseks. See annab ainult ühe sisendi, st T-sisendi. See flip-flop toimib lülitina Toggle. Lülitamine tähendab muutumist teiseks olekuks. T flip-flop on loodud kellaga RS-flipist.

Vooluringi skeem

T Flip Flopi ahel

T Flip Flopi tõetabel

T Flip Flopi tõetabel

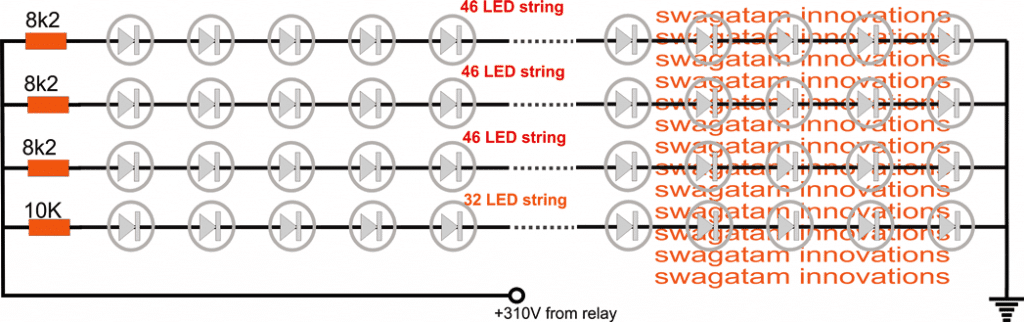

Elektrooniline ostsillaator

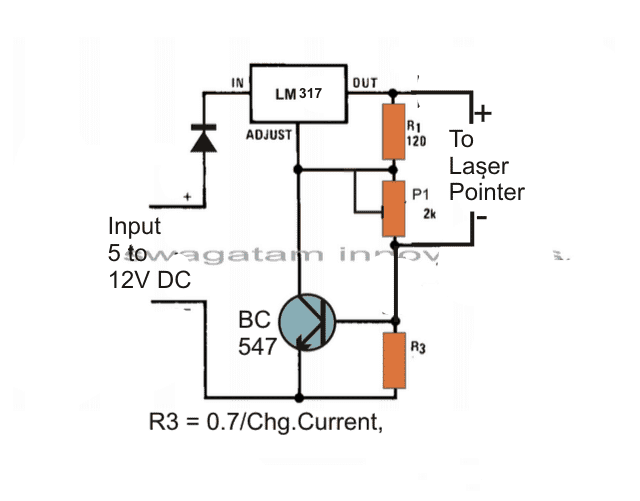

Elektrooniline ostsillaator on elektrooniline vooluahel, mis tekitab perioodilisi võnkuvaid signaale. Ostsillaator muundab toiteallikast alalisvoolu vahelduvvoolu signaaliks.

Elektrooniline ostsillaator

Ostsillaator on võimendi, mis annab tagasisidet sisendsignaaliga. See on mitte pöörlev seade vahelduvvoolu tootmiseks. Selleks, et ostsillaator ise juhtiks, tuleb sisendahelasse tagasi anda piisavalt energiat. Tagasiside signaal ostsillaatoris on regeneratiivne.

Elektroonilised ostsillaatorid liigitatakse kahte kategooriasse

- Sinusoidne ehk harmooniline ostsillaator

- Mitte-sinusoidne või lõõgastav ostsillaator

Sinusoidne ehk harmooniline ostsillaator

Siinuslainena väljundit andvaid ostsillaatoreid nimetatakse sinusoidseteks ostsillaatoriteks. Need ostsillaatorid suudavad väljundit pakkuda sagedustel vahemikus 20Hz kuni GHz. Sõltuvalt ostsillaatoris kasutatavast materjalist või komponentidest klassifitseeritakse sinusoidsed ostsillaatorid veel nelja tüüpi

- Häälestatud vooluringi ostsillaator

- RC ostsillaator

- Kristalli ostsillaator

- Negatiivse takistuse ostsillaator

Mitte-sinusoidne või lõõgastav ostsillaator

Mitte-sinusoidsed ostsillaatorid pakuvad väljundit ruudu-, ristkülikukujulise või saehamba kujul. Need ostsillaatorid võimaldavad väljundit sagedustel vahemikus 0 kuni 20 MHz.

Järjestikuste loogikalülituste rakendused

Järjestikuste loogikalülituste peamised rakendused on

- As loendur , vahetuste register, plätud.

- Kasutatakse mäluüksuse ehitamiseks.

- As programmeeritavad seadmed (PLD-d, FPGA, CPLD-d)

See kõik käib järjestikuste ahelate kohta. Järjestikused ahelad on vooluringid, kus väljundite vahetu väärtus sõltub sisendite vahetutest väärtustest ja ka olekutest, milles nad varem olid. Need sisaldavad mäluplokke ahela eelmise oleku salvestamiseks.

Lisaks võite selle artikliga seotud küsimuste või elektri- ja elektroonikaprojektide rakendamisel abi saamiseks pöörduda meie poole, kommenteerides allolevas kommentaaride jaotises. Siin on teile küsimus, Mida tähendab järjestikused ahelad?