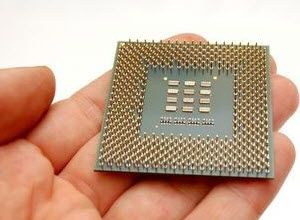

Oli ajastu, kus arvutid olid nii mammutmõõdulised, et nende paigaldamiseks oli vaja lihtsalt ruumi. Kuid täna on need nii arenenud, et me võime neid isegi sülearvutitena hõlpsasti kaasas kanda. Uuendus, mis selle võimaldas, oli integraallülituste kontseptsioon. Sisse Integraallülitused , suur hulk aktiivseid ja passiivsed elemendid koos nende ühendustega töötatakse välja väikese ränivahvli abil, mille ristlõige on tavaliselt 50–50 miili. Selliste vooluringide tootmise põhiprotsessid hõlmavad epitaksiaalset kasvu, maskeeritud lisandite difusiooni, oksiidide kasvu ja oksiidide söövitamist, kasutades mustri valmistamiseks fotolitograafiat.

Vahvli kohal olevate komponentide hulka kuuluvad takistid, transistorid, dioodid, kondensaatorid jne ... Kõige keerukam element, mida IC kaudu valmistada, on transistorid. Transistore on erinevat tüüpi nagu CMOS, BJT, FET. Transistoritehnoloogia tüübi, mida rakendada IC-ga, valime nõuete põhjal. Selles artiklis tutvustagem mõistet CMOS-i valmistamine (või) transistoride valmistamine CMOS-na.

CMOS-i valmistamine

Vähema võimsuse hajumise nõude jaoks CMOS-tehnoloogia kasutatakse transistoride rakendamiseks. Kui vajame kiiremat vooluahelat, on transistorid üle viidud IC kasutades BJT . Valmistamine CMOS-transistorid kuna IC-sid saab teha kolme erineva meetodiga.

N-süvendiga / P-süvendiga tehnoloogia, kus n-tüüpi difusioon toimub vastavalt p-tüüpi substraadil või p-tüüpi difusioon vastavalt n-tüüpi substraadil.

The Kakskaevu tehnoloogia , kus NMOS ja PMOS-transistor arendatakse üle plaadi samaaegse difusiooni teel epitaksiaalse kasvualuse, mitte substraadi kohal.

Silicon On Insulator protsess, kus selle asemel, et kasutada räni substraadina, kasutatakse isoleermaterjali, et parandada kiirust ja haardumistundlikkust.

N- kaevu / P- kaevu tehnoloogia

CMOS-i saab mõlemat integreerides NMOS ja PMOS transistorid sama räni vahvli kohal. N-kaevu tehnoloogias on n-tüüpi süvend hajutatud p-tüüpi substraadil, samas kui P-kaevus on see vastupidi.

CMOS-i valmistamise etapid

The CMOS-i valmistamise protsess voolama viiakse läbi kahekümne põhilise valmistamisetapiga, samal ajal kui see on valmistatud N-well / P-well-tehnoloogia abil.

CMOS-i valmistamine N-auku kasutades

Samm 1: Kõigepealt valime valmistamise aluseks substraadi. N-süvendi jaoks valitakse P-tüüpi räni substraat.

Aluspind

2. samm - oksüdeerimine: N-tüüpi lisandite selektiivne difusioon viiakse läbi, kasutades barjäärina SiO2, mis kaitseb vahvli osi substraadi saastumise eest. SiOkakson asetatud oksüdeerimisprotsessi abil, mis põhjustab substraadi kokkupuudet kõrgekvaliteedilise hapniku ja vesinikuga oksüdeerimiskambris umbes 1000 juures0c

Oksüdeerumine

3. samm - fotoresisti kasvatamine: Selektiivse söövitamise võimaldamiseks viiakse SiO2 kiht selles etapis läbi fotolitograafia. Selles protsessis kaetakse plaat ühtlase valgustundliku emulsiooni kilega.

Fotoresisti kasvatamine

4. samm - maskeerimine: See samm on fotolitograafia protsessi jätkamine. Selles etapis tehakse šablooni abil soovitud avatuse muster. Seda trafaretti kasutatakse maskina fotoresisti kohal. Substraat on nüüd avatud UV-kiired maski paljastatud piirkondade all olev fotoresist polümeriseerub.

Fotoresisti maskeerimine

5. samm - eksponeerimata fotoresisti eemaldamine: Mask eemaldatakse ja fotoresisti eksponeerimata piirkond lahustatakse, töötledes vahvlit, kasutades sellist kemikaali nagu trikloroetüleen.

Fotoresisti eemaldamine

6. samm - söövitamine: Vahvel kastetakse vesinikfluoriidhappe söövitavasse lahusesse, mis eemaldab oksiidi aladelt, mille kaudu dopante difundeeritakse.

SiO2 söövitamine

7. samm - kogu fotoresistkihi eemaldamine: Jooksul söövitamise protsess , see ei mõjuta neid SiO2 osi, mida fotoresistikiht kaitseb. Fotoresistlik mask eemaldatakse nüüd keemilise lahustiga (kuum H2SO4).

Fotoresistkihi eemaldamine

8. etapp - N-süvendi moodustamine: N-tüüpi lisandid hajutatakse p-tüüpi substraati läbi avatud piirkonna, moodustades N-süvendi.

N-kaevu moodustumine

9. etapp - SiO2 eemaldamine: SiO2 kiht eemaldatakse nüüd vesinikfluoriidhappe abil.

SiO2 eemaldamine

10. samm - polüoksiidi ladestumine: A värava vale joondamine CMOS-transistor tooks kaasa soovimatu mahtuvuse, mis võib vooluahelat kahjustada. Niisiis on selle „enesejoondatud väravaprotsessi” vältimiseks eelistatud juhul, kui värava piirkonnad moodustuvad enne allika ja äravoolu moodustumist ioonimplantatsiooni abil.

Polükristalli ladestumine

Polükristalli kasutatakse värava moodustamiseks, kuna see talub kõrgemat temperatuuri kui 80000c, kui vahvli allika ja äravoolu moodustamiseks kasutatakse lõõmutamismeetodeid. Polüsilikooni ladestatakse kasutades Keemilise sadestamise protsess õhukese väravaoksiidi kihi kohal. See polüoksiidkihi all olev õhuke väravaoksiid takistab värava piirkonnas edasist dopingut.

11. samm - väravapiirkonna moodustamine: Välja arvatud kaks väravat moodustamiseks vajalikku piirkonda NMOS ja PMOS transistorid ülejäänud osa polüsiidist eemaldatakse.

Väravapiirkonna moodustamine

12. samm - oksüdatsiooniprotsess: Vahvli kohale ladestub oksüdatsioonikiht, mis toimib edasise varjestusena difusiooni- ja metalliseerimisprotsessid .

Oksüdatsiooniprotsess

13. samm - maskeerimine ja difusioon: N-tüüpi lisandite difusioonipiirkondade valmistamiseks maskeerimisprotsessi abil tehakse väikesed lüngad.

Maskeerimine

Difusiooniprotsessi abil töötatakse NMOS-i terminalide moodustamiseks välja kolm n + piirkonda.

N-difusioon

14. samm - oksiidi eemaldamine: Oksiidikiht eemaldatakse.

Oksiidi eemaldamine

15. samm - P-tüüpi difusioon: Sarnaselt n-tüüpi difusiooniga PMOS-i klemmide moodustamiseks viiakse läbi ka p-tüüpi difusioon.

P-tüüpi difusioon

16. samm - paksu väljaoksiidi ladumine: Enne metallklemmide moodustamist asetatakse paks välioksiid, moodustades kaitsekihi vahvli piirkondadele, kus klemme pole vaja.

Paks välioksiidikiht

17. samm - metalliseerimine: Seda etappi kasutatakse metallklemmide moodustamiseks, mis võimaldavad ühendusi. Alumiinium levib kogu vahvlile.

Metalliseerimine

18. samm - liigse metalli eemaldamine: Liigne metall eemaldatakse vahvlist.

19. samm - terminalide moodustamine: Pärast liigse metalli eemaldamist moodustatud lünkades moodustatakse ühenduste jaoks klemmid.

Terminalide moodustamine

20. samm - terminalinimede määramine: Nimed määratakse ettevõtte terminalidele NMOS ja PMOS transistorid .

Terminalide nimede määramine

CMOS-i valmistamine P-kaevu tehnoloogia abil

P-süvendiga protsess sarnaneb N-süvendiga, välja arvatud see, et siin kasutatakse n-tüüpi substraati ja viiakse läbi p-tüüpi difusioone. Tavaliselt eelistatakse lihtsuse huvides N-kaevu protsessi.

CMOS-i kaks toru valmistamine

Kahetorulise protsessi abil saab kontrollida P- ja N-tüüpi seadmete võimendust. Programmiga seotud erinevad etapid CMOS-i valmistamine kasutades Twin-tube meetodit on järgmised

- Võetakse kergelt legeeritud n- või p-tüüpi substraat ja kasutatakse epitaksiaalset kihti. Epitaksiaalne kiht kaitseb kiibis olevat sulgemisprobleemi.

- Kasvatatakse mõõduka paksuse ja täpse lisandi kontsentratsiooniga kõrge puhtusega räni kihid.

- Torude moodustamine P- ja N-kaevu jaoks.

- Õhuke oksiidkonstruktsioon kaitseks saastumise eest difusiooniprotsessides.

- Allikas ja äravool moodustatakse ioonide implanteerimise meetoditega.

- Lõiked tehakse metallkontaktide osade valmistamiseks.

- Metalliseerimine toimub metallkontaktide tõmbamiseks

CMOS IC paigutus

Ülemine vaade CMOS-i valmistamine ja paigutus antakse. Siin saab erinevaid metallist kontakte ja N kaevu difusiooni selgelt vaadata.

CMOS IC paigutus

Seega on see kõik CMOS-i valmistamise tehnikad . Vaatleme ühe ruutu vahvlit, mis on jagatud 400 kiibiks, mille pindala on 50 miljonit 50 miljonit. Transistori valmistamiseks on vaja pindala 50 mil2. Seega sisaldab iga IC 2 transistorit, seega on igale vahvlile ehitatud 2 x 400 = 800 transistorit. Kui igas partiis töödeldakse 10 vahvlit, saab samaaegselt toota 8000 transistorit. Milliseid komponente olete IC-l täheldanud?